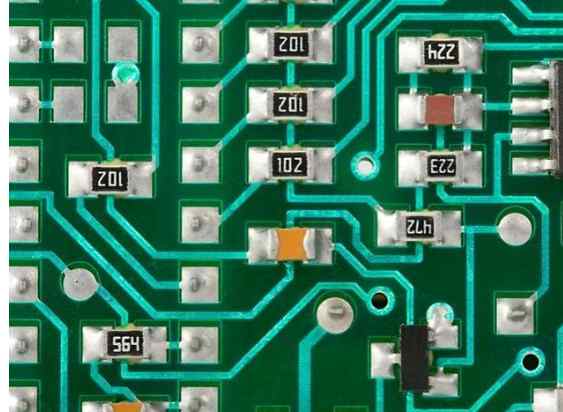

A very simple example is the rise time constraint, which is generally set to a constant of 1.5ns. From this condition, the maximum run length constraint can be obtained by multiplying 5,800mil/ns by 1.5ns rise time. A slightly more complex example is the component interval, which is determined by multiplying the tangent of the detection Angle by the height of the device. This calculation results in the minimum component interval.

Hierarchical management

One of the main benefits of parameterized constraints is that they can be processed hierarchically. For example, the global line width rule can be used as a PCB design constraint for the whole PCB design. Of course, there will be some areas or nodes that cannot follow this principle. In this case, the higher level constraint can be bypassed and the lower level constraint in the hierarchical PCB design can be used. Taking ACCEL Technologies' Constraint editor Solver as an example, there are seven levels of constraints:

1.PCB design constraints, for all objects without other constraints.

2. Hierarchical constraints, which apply to objects at a certain level.

3. The node type constraint applies to all nodes of a certain type.

4. Node constraints. This parameter is applicable to a node.

5. Interclass constraints, representing constraints between nodes of two classes.

6. Space constraint, used for all devices in a certain space.

7. Device constraint, used for a certain device.

The software follows the PCB design constraints in order from individual devices to the whole PCB design rules, and shows the application order of these rules in PCB design in a graphical way.

Example 1: Line width =f(impedance, layer spacing, dielectric constant, copper foil height)

Here is an example of how parametric constraints can be used as PCB design rules to control impedance. As mentioned above, impedance is a function of dielectric constant, distance from the nearest line layer, copper wire width and height. Since the impedance required by PCB design has been determined, these four parameters can be arbitrarily taken as related variables to write the impedance formula again. In most cases, the parameters that PCB designers can control are only the line width.

Because of this, the constraints on line width are functions of impedance, dielectric constant, distance to the nearest line layer, and copper foil height. If the formula is defined as the hierarchy constraint and the manufacturing process parameter is defined as the PCB design level constraint, then the software will automatically adjust the line width to compensate when the PCB design line layer changes. Similarly, if the PCB designed circuit board is produced by another process and the copper foil height changes, then the relevant rules in the PCB design level can be automatically recalculated by changing the copper foil height parameter.

Example 2: Device interval =max(default interval, f(device height, detection Angle))

The obvious benefit of using both parameter constraints and PCB design rule checking is that the parameterized approach is very portable and can be monitored when the PCB design is modified. This example shows how device spacing is determined by process characteristics and test requirements. The formula above indicates that device spacing is a function of device height and detection Angle.

Usually the detection Angle is a constant for the entire board, so it can be defined at the PCB design level. When testing by a different machine, the entire PCB design can be updated by simply entering a new value in the PCB design level. After the new machine performance parameters have been entered, the PCB designer can know if the PCB design is feasible by simply running the DRC to check whether the device spacing conflicts with the new spacing values, which is much easier than analyzing and correcting and then hard calculating according to the new spacing requirements.

Example 3: Component layout

In addition to organizing PCB design objects and constraints, PCB design rules can also be used for component layout, i.e. they can detect where to place components based on constraints without introducing errors.

In fact, generating constraints in a modular manner can greatly improve their maintainability and reusability. New expressions can be generated by referring to the constraint parameters of different layers in the previous stage. For example, the top layer line width depends on the top layer distance and copper wire height, and the variables Temp and Diel_Const in the PCB design level. Note that PCB design rules are displayed in descending order. Changing a higher constraint immediately affects all expressions that refer to that constraint.

PCB design reuse and documentation

Parameterized constraints not only significantly improve the initial PCB design process, but are also more useful for engineering changes and PCB design reuse. Constraints can be part of the PCB design, system, and documentation that, if not kept in the minds of engineers or PCB designers, may be slowly forgotten when they move on to other projects. Constraint documents document the electrical performance rules to be followed during the PCB design process and provide an opportunity for others to understand the PCB designer's intentions so that these rules can be easily applied to new manufacturing processes or changed to meet electrical performance requirements. Future multiplexers can also know the exact PCB design rules and make changes by inputting new process requirements without having to guess at things like how the linewidth was obtained.

Conclusion of this paper

The parameter constraint editor facilitates PCB layout and wiring under multi-dimensional constraints, and for the first time, enables automatic routing software and PCB design rules to be fully checked against complex electrical and process requirements, rather than relying solely on experience or simple and less useful PCB design rules. The result is that PCB design can be a success, reducing or even eliminating prototype debugging.