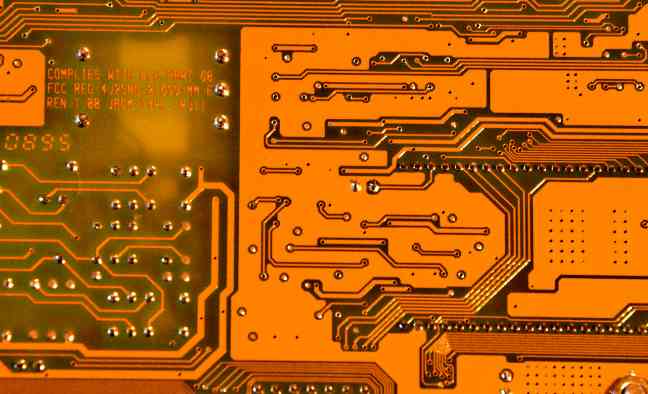

In the design of the PCB board, the anti-ESD design of the PCB can be achieved through layering, proper layout and wiring and installation. During the design process, the vast majority of design modifications can be limited to adding or subtracting components through prediction. By adjusting the PCB layout and wiring, ESD can be well prevented.

Here are some common precautions.

1, as far as possible to use multi-layer PCB, relative to double-sided PCB, the ground plane and power plane, as well as the closely arranged signal line - ground line spacing can reduce the common mode impedance and inductive coupling, so that it reaches 1/10 to 1/100 of the double-sided PCB. Try to place each signal layer next to a power layer or ground layer. For high-density PCBS that have components on both the top and bottom surfaces, have very short connection lines and many filling places, you can consider using an inner line.

2, as far as possible to put all connectors aside.

3. If possible, introduce the power cord from the center of the card and away from the area that is easily directly affected by ESD.

4. On all PCB layers under the connectors that lead out of the chassis (easy to be directly hit by ESD), wide chassis floors or polygon filling floors should be placed and connected together with holes at intervals of about 13mm.

5. Place mounting holes on the edge of the card, and connect the top and bottom pads of the frictionless flux around the mounting holes to the ground of the chassis.

6, PCB assembly, do not apply any solder on the top or bottom pad. Use screws with built-in washers to achieve tight contact between the PCB and the metal case/shield or ground surface bracket.

7. At the top and bottom of the card near the mounting holes, connect the chassis floor and circuit floor together with 1.27mm wide wires along the chassis ground wire every 100mm. Adjacent to these connection points, a pad or mounting hole for mounting is placed between the chassis floor and the circuit floor. These ground connections can be cut open with a blade to stay open, or a jump with a magnetic bead/high frequency capacitor.

8, if the circuit board will not be placed in the metal chassis or shielding device, the top and bottom of the circuit board chassis ground wire can not be coated with solder, so that they can be used as ESD arc discharge electrode.

9, to set up a ring around the circuit in the following way:

10, In the area that can be directly hit by ESD, a ground line should be laid near each signal line.

11, the I/O circuit should be as close as possible to the corresponding connector.

12, the circuit susceptible to ESD should be placed in the area near the center of the circuit, so that other circuits can provide them with a certain shielding effect.

13, usually placed in the receiving end of the series of resistors and magnetic beads, and for those easy to be ESD cable drivers, you can also consider placing a series of resistors or magnetic beads at the drive end.

14. A transient protector is usually placed at the receiving end. Connect a short, thick wire (less than 5 times the width, preferably less than 3 times the width) to the chassis floor. The signal and ground wires coming out of the connector are connected directly to the transient protector before they can be connected to the rest of the circuit.

15. The filter capacitor should be placed at the connector or within a range of 25mm from the receiving circuit.

16. Make sure the signal line is as short as possible.

17, when the length of the signal line is greater than 300mm, be sure to parallel a ground wire.

18. Ensure that the loop area between the signal line and the corresponding loop is as small as possible. For long signal lines, the position of the signal line and the ground line should be changed every few centimeters to reduce the loop area.

19, drive signals from the center of the network into multiple receiving circuits.

20, ensure that the loop area between the power supply and the ground is as small as possible, and place a high-frequency capacitor near each power pin of the integrated circuit chip.

21. Place a high-frequency bypass capacitor within 80mm of each connector.

22, where possible, to fill unused areas, all layers of fill every 60mm distance to connect the ground.

23, ensure that the ground is connected at the two opposite end points of any large ground filling area (approximately greater than 25mm×6mm).

24, When the length of the opening on the power or ground plane exceeds 8mm, the two sides of the opening should be connected with a narrow line.