Relevant rules for PCB design of high-speed converter

Q: What are the important PCB layout and routing rules when using high-speed converters?

Answer: In order to ensure that the design performance meets the technical specifications of the data manual, some guidelines must be followed. First of all, there is a common question: "Should AGND and DGND ground planes be separated?" The simple answer is: It depends.

The detailed answer is: usually not separate. Because in most cases, separating the ground plane will only increase the inductance of the return current, which brings more disadvantages than advantages. It can be seen from the formula V=L (di/dt) that the voltage noise will increase with the increase of inductance. As the switching current increases (because the sampling rate of the converter increases), the voltage noise will also increase. Therefore, the ground plane should be connected together.

For example, in some applications, in order to meet the requirements of traditional design, dirty bus power or digital circuits must be placed in some areas. At the same time, due to size constraints, the circuit board cannot be well divided. In this case, separating the ground plane is the key to achieving good performance. However, in order for the overall design to be effective, these grounding layers must be connected together through a bridge or connection point somewhere on the circuit board. Therefore, the connection points should be evenly distributed on the separated ground plane. Finally, there is often a connection point on the PCB that becomes the best location for the return current to pass without causing performance degradation. This connection point is usually located near or below the converter.

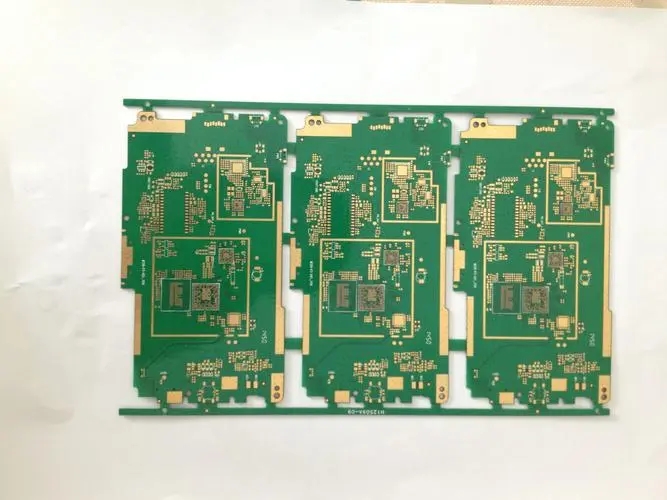

When designing power supply layers, all copper wires that can be used in these layers shall be used. If possible, do not allow these layers to share wiring, because additional wiring and vias will divide the power layer into smaller pieces, quickly damaging the power layer. The resulting sparse power layer can squeeze current paths to the place where they are most needed, that is, the power supply pin of the converter. The current between the squeeze vias and the routing wire will increase the resistance, resulting in a slight voltage drop across the power supply pins of the converter.

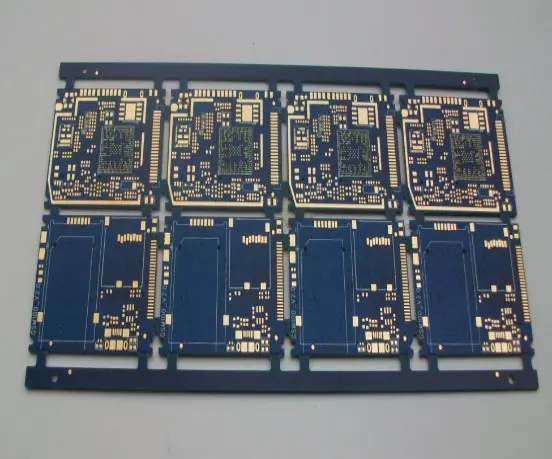

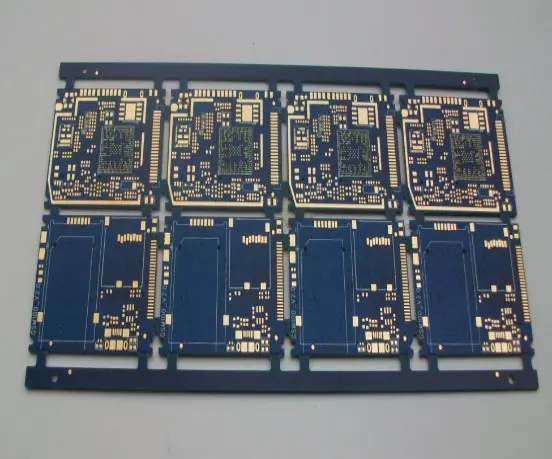

Finally, the placement of the power supply layer is very important. Do not stack the high noise digital power supply on the analog power supply layer. Otherwise, although they are located on different layers, they may still be coupled. To minimize the risk of system performance degradation, these types of layers should be separated rather than stacked together as much as possible in the design.

At the same time, the task of discussing the power transmission system (PDS) design of printed circuit board (PCB) is often ignored, but it is crucial for system level analog and digital designers.

The design objective of PDS (Power Transmission System) is to minimize the voltage ripple generated in response to the power supply current demand. All circuits require current. Some circuits require a large amount of current, while others need to provide current at a faster rate. The use of fully decoupled low impedance power or ground layers and good PCB stacking can minimize the voltage ripple generated by the current demand of the circuit. For example, if the designed switching current is 1A and the impedance of PDS is 10m Ω, the maximum voltage ripple is 10mV.

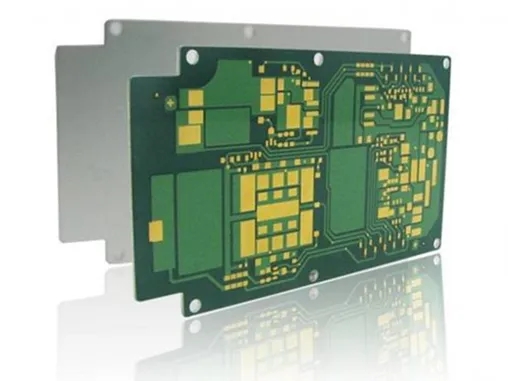

First, we should design a PCB stack structure that supports larger layer capacitors. For example, a six layer stack may include a top signal layer, a first ground layer, a first power layer, a second power layer, a second ground layer, and a bottom signal layer. It is specified that the first ground plane and the first power layer are close to each other in the stack structure, and the spacing between the two layers is 2 to 3 mils, forming an inherent layer capacitance. The biggest advantage of this capacitor is that it is free and only needs to be noted in the PCB manufacturing notes. If the power supply layer must be divided, and there are multiple VDD power rails on the same layer, the largest power supply layer should be used. Don't leave holes, and pay attention to sensitive circuits. This will maximize the capacitance of the VDD layer. If the design allows additional layers (in this case, from six layers to eight layers), two additional ground layers should be placed between the first and second power layers. When the core spacing is also 2 to 3 mils, the inherent capacitance of the laminated structure will be doubled.

For an ideal PCB stack, decoupling capacitors should be used at the starting entry point of the power layer and around the DUT, which will ensure that the PDS impedance is low throughout the frequency range. Use several 0.001 μ F to 100 μ The capacitance of F helps to cover this range. It is unnecessary to configure capacitors everywhere; Capacitance facing DUT docking will break all manufacturing rules. If such severe measures are required, it indicates that there are other problems in the circuit. Circuit board assembly, circuit board design, and circuit board processing manufacturers explain the rules related to high-speed converter PCB circuit board design.