As a microelectronic IC learner, there is also a course in this semester: "Microelectronic devices", today I will talk about the basic devices: CMOS devices and circuits. We'll talk about latches and triggers later.

Today's main content is as follows:

· Brief introduction of MOS transistor structure and working principle

·CMOS unit circuit and layout

·CMOS gate circuit

· Power representation of CMOS

To be honest, CMOS is more micro electronic devices, micro electronic devices are really difficult... Here are a few things you might want to know about doing digital design (I'll add more later if necessary).

1. Brief introduction of structure and working principle of MOS transistor

It is more or less known that the main function of a transistor in a digital circuit is an electronic switch, which is turned on or off by a voltage or a current. There are roughly two kinds of transistors: One is bipolar junction transistor and the other is metal-oxide-semiconductor field-effect transistor (MOSFET or MOS). metal-oxide-semiconductor field effect transistor). Here we mainly talk about MOS, BJT in the current digital IC design is not the mainstream technology.

①MOS transistors are divided into PMOS and NMOS, which kind of MOS depends on the substrate and doping concentration. As for how it is formed, it is too complicated to explain in a few words, so let's skip it and look directly at their cross section diagram and briefly explain how they work (NMOS are taken as examples below).

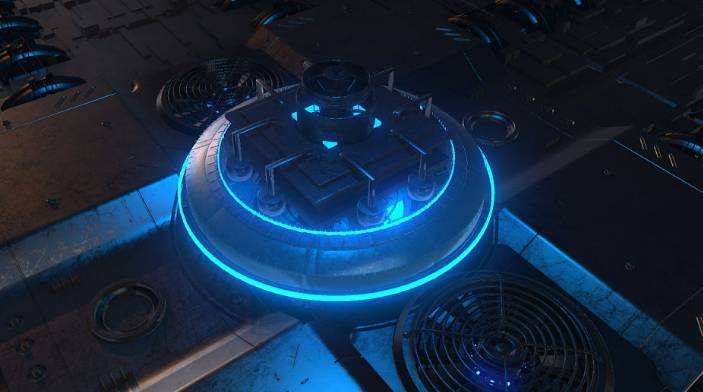

The cross-sectional structure of the NMOS transistor is shown as follows:

IC design: CMOS devices and their circuits

The substrate is a silicon substrate (where the Body Si is), the top is a conductive gate, and the middle is an insulating layer composed of silica. In the past, the gate * was made of metal, so it was called metal-oxide-semiconductor. Now the gate * uses poly. In the MOS structure, a capacitor is formed by silica between a metal (polysilicon) and a semiconductor substrate.

Well, it doesn't matter if you don't understand the above paragraph, but remember that in the above NMOS transistor, the substrate is P-type, and there are two N-type doping regions on the substrate called Source and Drain. (You can define the left side as the drain and the right side as the source.) Since the device is symmetrical at this time, S and D are not really determined until the power supply and ground are connected), the upper middle is called Gate * (Gate), which is the three electrodes of NMOS (actually MOS is a 4-terminal device, and its substrate is also a terminal). Here's how they work.

We have said that the function of a transistor is roughly a switch that turns on and off under the control of a current or voltage. In the case of an NMOS transistor, we now apply a voltage to it to make it work:

IC design: CMOS devices and their circuits

As shown in the upper left figure, the so-called source *, when applied with voltage, is equivalent to the source of electrons; The so-called leakage *, is equivalent to the leakage of the electron opening; And the grid in the middle, *, acts like a control switch: On the one hand, by controlling the high level voltage applied in the grid *, there is a channel between the source and drain, and the electrons flow from the source to the drain through the channel, and the direction of the current is from the drain to the source, so as to conduct electricity, that is, when the "switch" is opened (due to the formation of N channel, that is, electronic conduction, so it becomes N-type CMOS). On the other hand, a low level voltage is applied to the gate by the control, so that the channel is off, so that the source and drain are off, that is, when the "switch" is off. This is the structure and workflow of NMOS. (PMOS work in the opposite way: turn on by controlling the low level voltage applied to the gate, and turn off the channel by controlling the high level voltage applied to the gate.)

Note: When the voltage of the gate * reaches a certain value, the channel will be formed. The voltage when the channel is formed is called the threshold voltage (Vth).

② Let's take a look at the I-V characteristic curve (note the two names, one is transfer characteristic curve, one is output characteristic curve) :

IC design: CMOS devices and their circuits

In * we know that for NMOS, the source *(S) is grounded, the drain *(D) is connected to the digital power supply, at work, the general Vds is constant, and then according to the voltage on the gate *(G) to determine whether the channel is open. When working, the value of Vg (that is, the voltage value of the input signal) is a fixed value, which is either high level (may fluctuate) or low level. From here, we also know that when NMOS works, there is current flowing from the power supply (VDD) to the ground (that is, from D to S). When the power supply voltage is constant, This current follows the voltage across the gate *.

③ Then we look at the internal capacitance formed by itself (parasitic capacitance) of MOS.