There are many ways to solve EMI problems. Modern EMI suppression methods include: using EMI suppression coating, selecting suitable EMI suppression parts and EMI simulation design. Starting from the most basic PCB layout, this paper discusses the role and design skills of PCB stacking in controlling EMI radiation.

Power bus

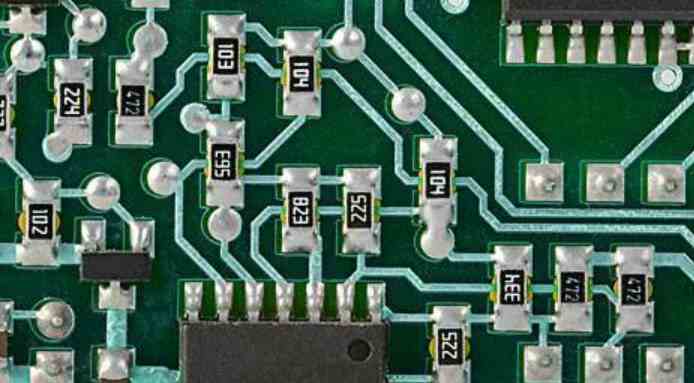

Reasonable placement of the appropriate capacity of capacitors near the IC's power pin, PCB manufacturing can make the IC output voltage jump faster. Due to the limited frequency response nature of capacitors, this prevents them from generating the harmonic power needed to drive the IC output cleanly over the full frequency band. In addition, the transient voltage formed on the power bus will form a voltage drop on the inductor ends of the decoupling path, and these transient voltages are the main common mode EMI interference sources.

In terms of the IC on the circuit board, the power layer around the IC can be regarded as a good high-frequency capacitor, which can collect the part of the energy leaked by the discrete capacitor that provides high frequency energy for clean output. In addition, the inductance of a good power layer is small, so that the transient signal synthesized by the inductor is also small, thereby reducing common mode EMI.

The connection from the power layer to the IC power pin must be as short as possible because the digital signal is rising faster and faster, preferably directly to the pad where the IC power pin is located.

In order to control common mode EMI, the power layer to help decouple and have a sufficiently low inductance, PCB proofing this power layer must be a reasonably well-designed power layer pairing. So, how much is good? The answer depends on the layering of the power supply, the material between the layers, and the operating frequency (that is, a function of the IC rise time). Typically, the spacing of the power layer is 6mil, and the interlayer is FR4 material, so the equivalent capacitance per square inch of the power layer is about 75pF. Obviously, the smaller the layer spacing, the larger the capacitance.

At the current rate of IC development, devices with rise times in the range of 100 to 300ps will occupy a high proportion. For circuits with 100 to 300ps rise times, 3mil layer spacing will no longer be appropriate for most applications. At that time, it is necessary to adopt layering techniques with layer spacing of less than 1mil and replace the FR4 dielectric material with a material with a high dielectric constant. Now, ceramics and Gatao plastics can meet the design requirements of 100 to 300ps rise-time circuits.

For today's common 1 to 3ns rise time circuits, 3 to 6mil layer spacing and FR4 dielectric materials, it is usually able to handle high-end harmonics and make the transient signal low enough, that is, common mode EMI can be dropped very low. The PCB layer-stack design examples presented in this article will assume layer spacing of 3 to 6mil.

Electromagnetic shielding

From the point of view of signal wiring, a good layering strategy should be to place all signal wiring in one or several layers, which are next to the power layer or ground layer. For power supplies, a good layering strategy should be that the power layer is adjacent to the ground layer, and the distance between the power layer and the ground layer is as small as possible.

LED display PCB why should brush three anti-paint

Three anti-paint is also called PCB electronic circuit board protective oil, coating oil, moisture-proof paint, three anti-paint, waterproof glue, insulating paint, anti-corrosion paint, anti-salt spray paint, dust-proof paint, protective paint, coating paint, three anti-glue, etc. The PCB circuit board of the LED display screen using the three anti-paint has the performance of waterproof, moisture-proof, dustproof and cold and heat shock resistance, aging resistance, radiation resistance, salt spray resistance, ozone corrosion resistance, vibration resistance, good flexibility, strong adhesion and other properties.

Moisture is the most prevalent and destructive main factor on PCB boards. Excessive moisture will greatly reduce the insulation resistance between conductors, accelerate high-speed decomposition, reduce Q value, and corrode conductors. We often see the patina on the metal part of the PCB circuit board is not coated with three anti-paint metal copper and water vapor, oxygen caused by its chemical reaction.

And hundreds of contaminants found casually on printed circuit boards can be just as destructive. They can cause the same effects as moisture erosion - electron decay, corrosion of conductors and even irreversible short circuits. The contaminants most commonly found in electrical systems may be caused by chemicals left over from the process. Examples of these contaminants are fluxes, solvent release agents, metal granules and mark inks. There are also major contamination groups caused by human careless handling, such as human oil, finger marks, cosmetics and food residues. There are also many contaminants in the operating environment, such as salt sprays, sand, fuels, acids, and other corrosive vapors and molds.

The three anti-paint coating on the printed circuit board and components can reduce or eliminate the deterioration of electronic operating performance when it may be affected by adverse factors in the operating environment. If the coating can maintain its effect for a satisfactory period of time, such as longer than the service life of the product, it may be considered to have fulfilled its coating purpose.

Even if the coating layer is very thin, it can withstand mechanical vibration and swing, thermal shock, and operation at high temperatures to a certain extent. Of course, the idea that thin films can be used to give mechanical strength or adequate insulation to individual parts inserted into printed circuit boards is wrong. The components must be mechanically inserted and must have their own suitable caulking agent, so that there is double insurance against accidents.